DE1-SoC My First FPGA PDF manual

Note: Do not use spaces in any file or directory names!

Sample instructions for creating SOF

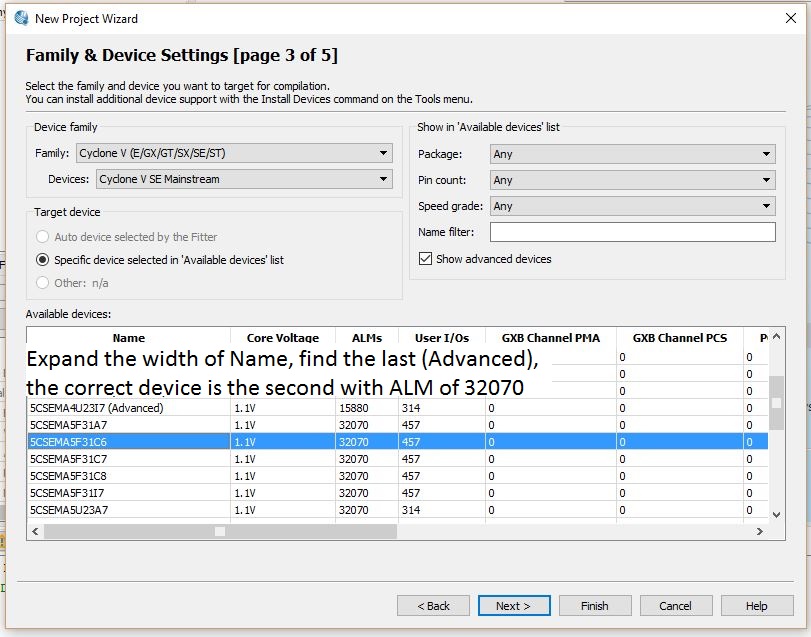

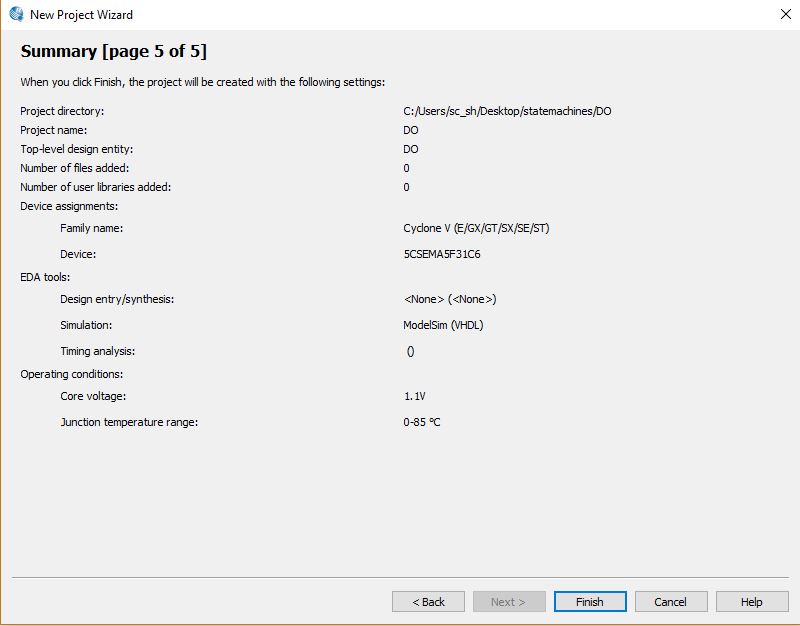

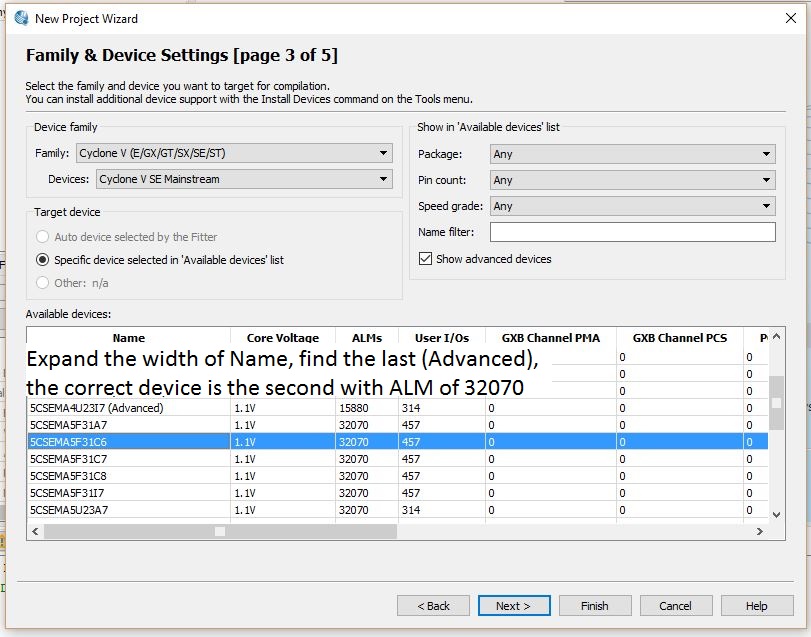

New Project Wizard, Family & Device Settings [page 3 of 5]

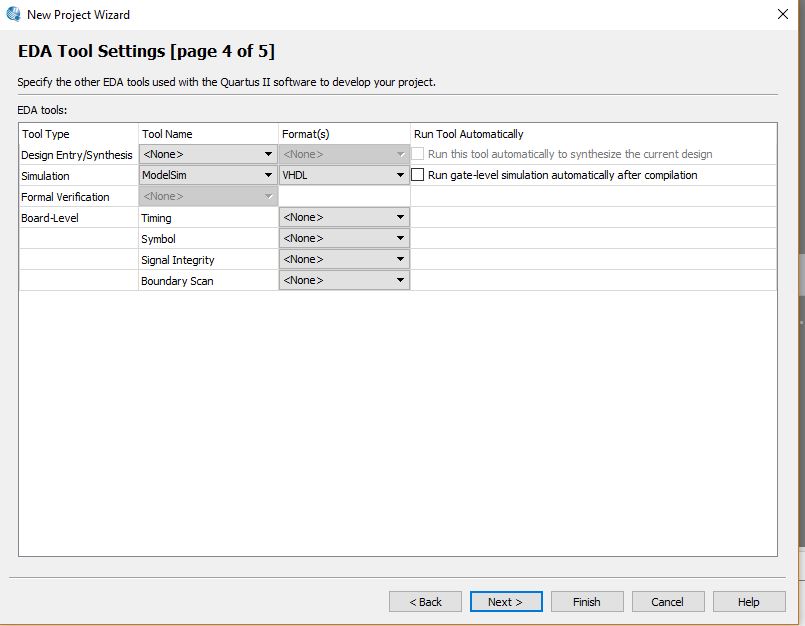

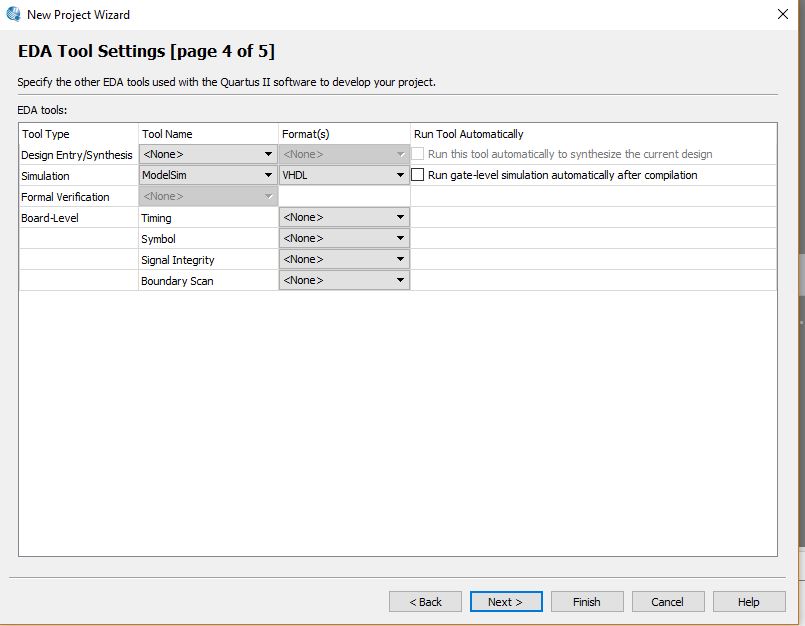

New Project Wizard, EDA Tool Settings [page 4 of 5]

- File > New Project Wizard, Next

- Add Files, Next

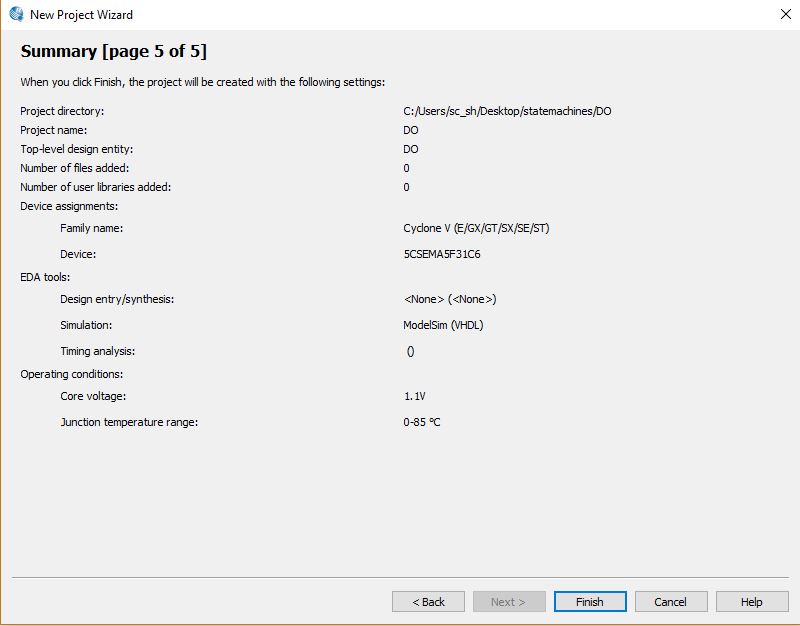

- Name of this Project: DoorOpener

- Device Family: Cyclone V (E/GX/GT/SX/SE/ST)

- Devices: Cyclone V SE Mainstream

- Select device: 5CSEMA5F31C6, Next, Next

- Simulation Tool Name: ModelSim, Format: VHDL

- Uncheck "Run gate-level simulation automatically after compilation", Next

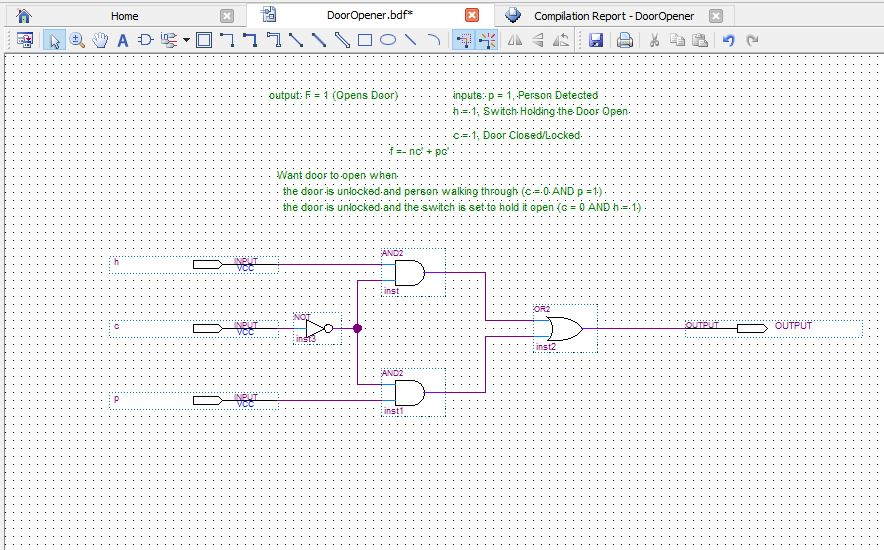

- File > New > Block Diagram/Schematic File

- Finish

- File | New | Block Diagram/Schematic File", OK

- File | Save As

- Default name is ok; Save

- Enter symbols to match

- Add to project with: Project | Add Current File to Project

- Compile the design: Processing | Start Compilation

- Create system in HDL VHDL with File | Create/Update | Create HDL Design File from Current File; be sure to select the bdf first

- Select "VHDL" as File type; click on OK

- Open your newly created VHDL file: File | Open File, DoorOpener.vhd

- Select DoorOpen.vhd; Add to project with: Project | Add Current File to Project

- Remove the bdf file from the Project, but do NOT delete the file from the filesystem: Project | Add/Remove Files from Project; select DoorOpener.bdf and delete

- Note: If you did not select the device, do so now with: Assignments | Device

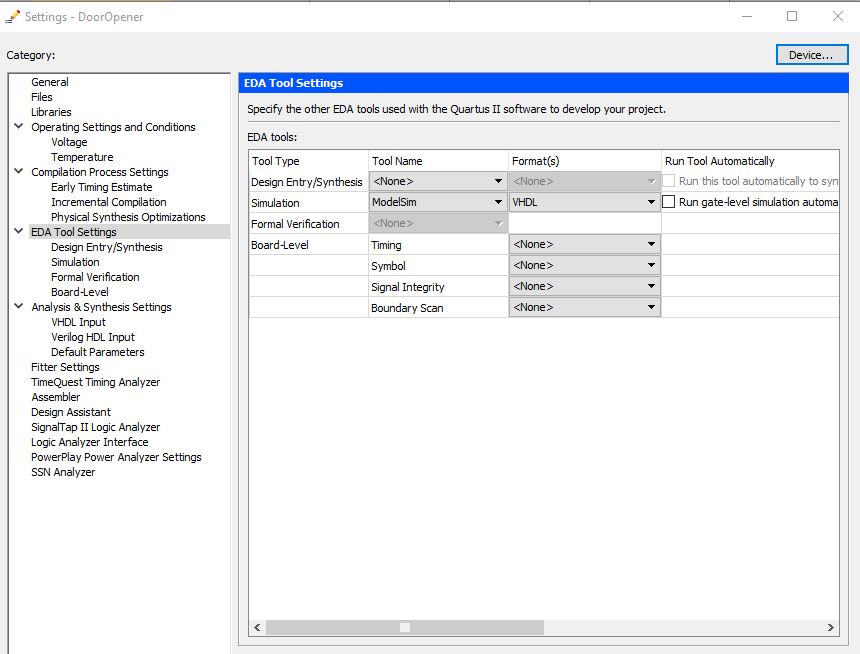

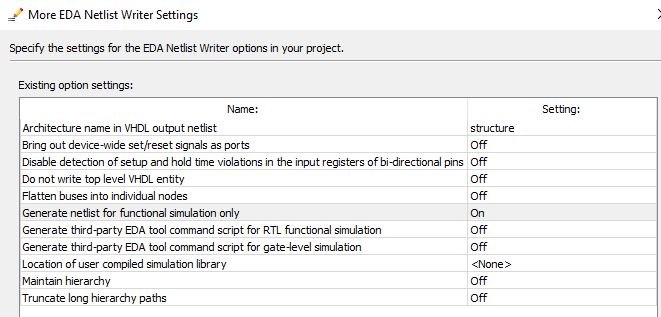

- Compare the settings via Assignment | Settings, EDA Tool Settings, Simulation with

- Select Simulation, "More EDA Netlist Writer Settings"

- Turn on Generate netlist for functional simulation only; you need to click/double click on "Off" in order to select "On"; select OK

- Note: I did not use "user compiled simulation library"

- Note: I also did not change "More NativeLink Settings"

- Check EDA Tools setting in: Tools | Options | EDA Tool Options

- ModelSim: c:\Modeltech_pe_edu_10.4a\win32pe_edu\

- ModelSim-Altera: c:\altera\13.1\modelsim_ase\win32aloem\

- Compile the circuit for functional simulation: Processing | Start | Start Analysis & Elaboration

- Create testbench: Processing | Start | Start Test Bench Template Writer

- Note: You may need to select "all files"; Open file in simulation\modelsim, called DoorOpener.vht

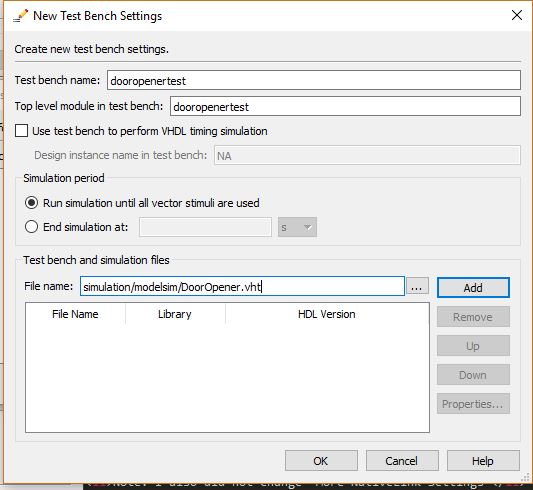

- After adding simulation statements, change settings to include your testbench: Assignments | Settings, EDA Tool Settings, Simulation

- Select radio button "Compile test bench", click on "Test Benches", then "New"

- Choose testbench name, here is "dooropenertest", add "dooropener.vht"; click on "..." to select vht file

- Click "Add", and then "OK". and then "ok" on previous menu, and finally "ok" on the Settings menu

- Select the vht file, then add to the project with Project | Add Current File to Project

- After anytime you change the simulation (or after creating), must prepare with: Processing | Start | Start Analysis & Elaboration

- To run the simulation: Tools | Run Simulation Tool | RTL Simulation

- Now, from the ModelSim program, expand "Model" by clicking on the plus sign

- Simulate | Start Simulation

- Select the testbench entry, dooropener_vhd_tst, click "ok"

- If you were using actual board pins, you would assign them with: Assignments | Pin Planner

- Tools > Programmer

- Click Auto Detect

- Select 5CSEMA5 and click OK

- Select SCSEMA5F31; click Change File

- Note: the FPGA is the SCSEMA5 icon

- Note: the HPS is the SOCVHPS icon

- Click on Program/Configure tab

- Press Start button

Optional: Test with stand alone ModelSim PE Student Edition, 10.4a

- Change to the current directory with: File | Change Directory

- Create new library: File | New | Library Use default name of "work"

- Compile simulation file created previously: Compile | Compile simulation\modelsim\ DoorOpener.vht

- Verify that there are no errors in the command line interupter

- Optional: compile the cli with: vcom -reportprogress 300 -work work c:/Users..../simulation/modelsim/DoorOpenerTest.vht